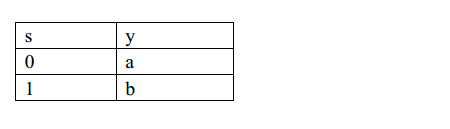

设计一个 2 选 1 多路选择器。进一步熟悉 Verilog HDL 设计流程,组合电路的设计和测试。 在数字信号的传输过程中,有时需要从多路输入数据中选出某一路数据,完成此功能的逻辑器件称为数据选择器,即所谓多路开关,简称 MUX (Multiplexer)。2 选 1 多路选择器能在选择信号的控制下,从 2 路输入信号中选择其中的一路数据送到输出口。其真值表如下表所示。 为了完成判断学生成绩等级的任务,编写的程序要能根据s输入的值给出相应y输出的值,满足多路选择器的真值表 测试平台:EduCoder 觉得有帮助的可以点个赞再走哦!!

任务描述

相关知识

逻辑原理

多路选择真值表

编程要求

源代码

module mux21(a,b,s,y); input a,b,s; output y; reg y; always @(a,b,s) // 请在下面添加代码,实现当选择信号S为0时选中a,为1时选中b; /********** Begin *********/ begin case(s) 1'b0:begin y = a;end 1'b1:begin y = b;end default:begin y = 0;end endcase end /********** End *********/ endmodule

本网页所有视频内容由 imoviebox边看边下-网页视频下载, iurlBox网页地址收藏管理器 下载并得到。

ImovieBox网页视频下载器 下载地址: ImovieBox网页视频下载器-最新版本下载

本文章由: imapbox邮箱云存储,邮箱网盘,ImageBox 图片批量下载器,网页图片批量下载专家,网页图片批量下载器,获取到文章图片,imoviebox网页视频批量下载器,下载视频内容,为您提供.

阅读和此文章类似的: 全球云计算

官方软件产品操作指南 (170)

官方软件产品操作指南 (170)