2.CPU 访问内存的过程 这里为啥要把那一行都 read 到 buffer 中呢? 还不是为了提高访问速度,如果 cpu 下次访问的数据还在那一行则直接从缓存中读取出来。 那如果不是呢? 小结:

目录:

===========================================

先来看一下能存一个字节(1)的逻辑门电路:

当B为 1 时,无论 A的输入是啥,输出都是1。这也就意味着这个异或逻辑门电路能存一个字节为 1 的数据。

在来看一个能存 0 的逻辑门电路:

同样的当B=0 时,无论 A 输入是啥,此时的 out = 0 的。

我们都知道计算机处理的数据是二进制的也即0和1,所以我们将 AND 和 OR 逻辑门电路组成起来,就可存二进制的数据了。

组合起来的逻辑门电路如下:

SET 端就是用来数据输入的,而 RESET 顾名思义就是复位用的。我们将这个逻辑门电路装在一个黑箱子后:

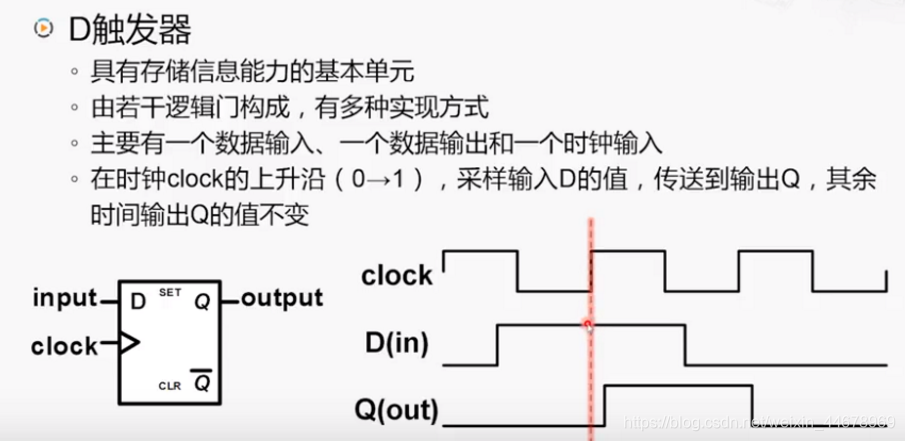

我们将8个门锁组合在一起就能构造一个寄存器(D触发器)。

PS:D触发器的原理

这样感觉是不是这很抽象? 那我们举个栗子:

那么你会问内存跟寄存器又有啥关系? 怎么感觉一点关系都没有呢?

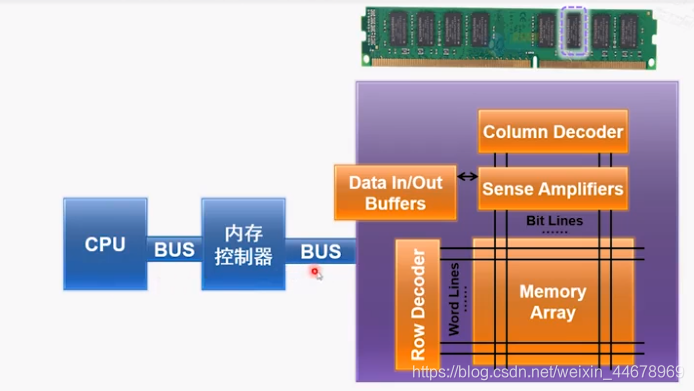

你可以这样理解,我们将许多的寄存器(10亿够不够?)组成矩阵。这样多个矩阵就能组成内存了。这里我将内存条放大,有个感性的认识。

有没有看到放大最后的那张照片,里面就是组成的矩阵。哈哈,现在是不是有点理解了?

(1) BUS Request

申请地址总线的控制权,将访问的地址发送给 MMU (内存控制器/内存管理单元) 。 MMU 将地址分解成 row 和 column 地址。

(2) [ Precharge ] and Row Access

即预充电 (后面说) 和行访问,MMU 通过 BUS 将 row 发送给 Row Decoder 使其激活要访问的那一行。

(3)Column Access

列访问,MMU 通过 BUS 将 column 发送给 Column Decoder 使其激活要访问的那一列。将(row,column)所指向的那一行数据 通过 Sens Amplifiers(读出放大器)read 到 Data in/out Buffer 中。

(4) Bus Transmission

总线传输(row,column)所代表的数据。

则将读取出来那一行的状态使其失效即可。 — Precharge (预充电)

其实从硬件在到逻辑角度理解内存就发现 哦? 原来内存内部构造是这样的呀。

本网页所有视频内容由 imoviebox边看边下-网页视频下载, iurlBox网页地址收藏管理器 下载并得到。

ImovieBox网页视频下载器 下载地址: ImovieBox网页视频下载器-最新版本下载

本文章由: imapbox邮箱云存储,邮箱网盘,ImageBox 图片批量下载器,网页图片批量下载专家,网页图片批量下载器,获取到文章图片,imoviebox网页视频批量下载器,下载视频内容,为您提供.

阅读和此文章类似的: 全球云计算

官方软件产品操作指南 (170)

官方软件产品操作指南 (170)